# Welcome to 048704/236803 Seminar on Coding for Non-Volatile Memories

# 1956: IBM RAMAC5 Megabyte Hard Drive

Above: An IBM Model 350 Disk File being delivered. Yes, that's ONE hard disk drive unit.

#### A 2014 Terabyte Drive

Some of the main goals in designing a computer storage: Price Capacity (size) Endurance Speed **Power Consumption**

# The Evolution of HDD

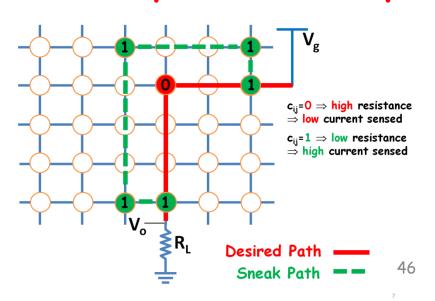

#### **Disk Drive Basics**

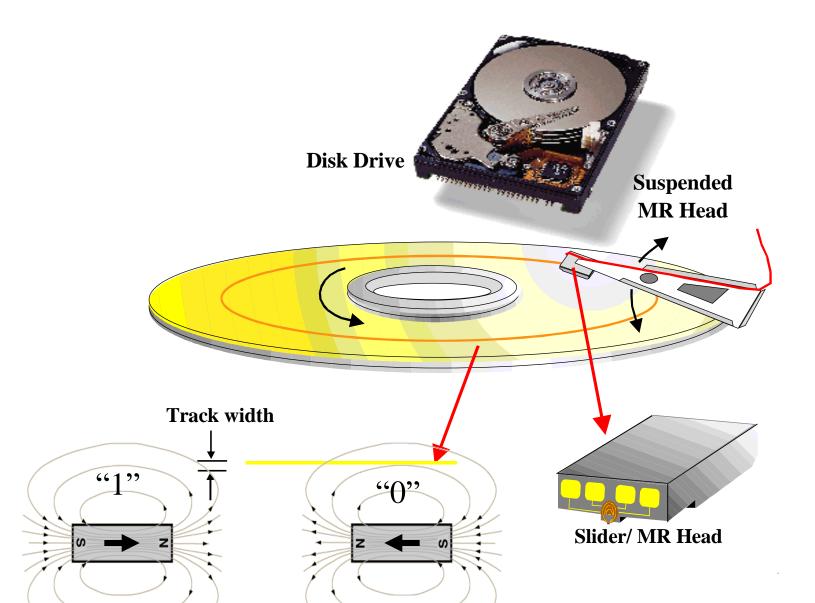

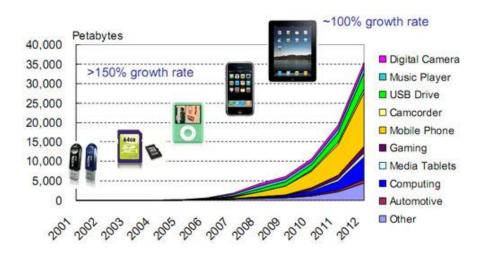

# Memories Today

- RAM memories, DRAM, SRAM

- Hard disk

- Tape

- Floppy disk

- Optical disc: CD, DVD, BlueRay

- Punch cards

- Flash memories

- Phase change memories

- Memristors/STTRAM/MRAM

#### Non-Volatile Memories

Volatile

Memories

TECHNOLOGIES

inside

# Fast Low Power Reliable

~10<sup>5</sup> P/E Cylces

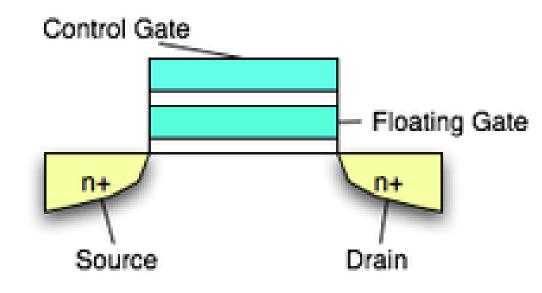

# Flash Memory Cell

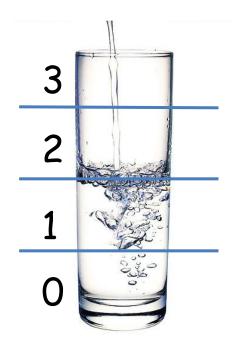

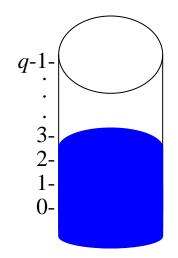

# Multi-Level Flash Memory Model

- Array of cells, made of floating gate transistors

- Each cell can store q different values.

- Today, q typically ranges between 2 and 16.

# Multi-Level Flash Memory Model

- Array of cells, made of floating gate transistors

- Each cell can store q different values.

- Today, **q** typically ranges between **2** and **16**.

- The cell's level is increased by pulsing electrons.

- Reducing a cell level requires resetting all the cells in its containing block to level 0 A VERY

EXPENSIVE OPERATION

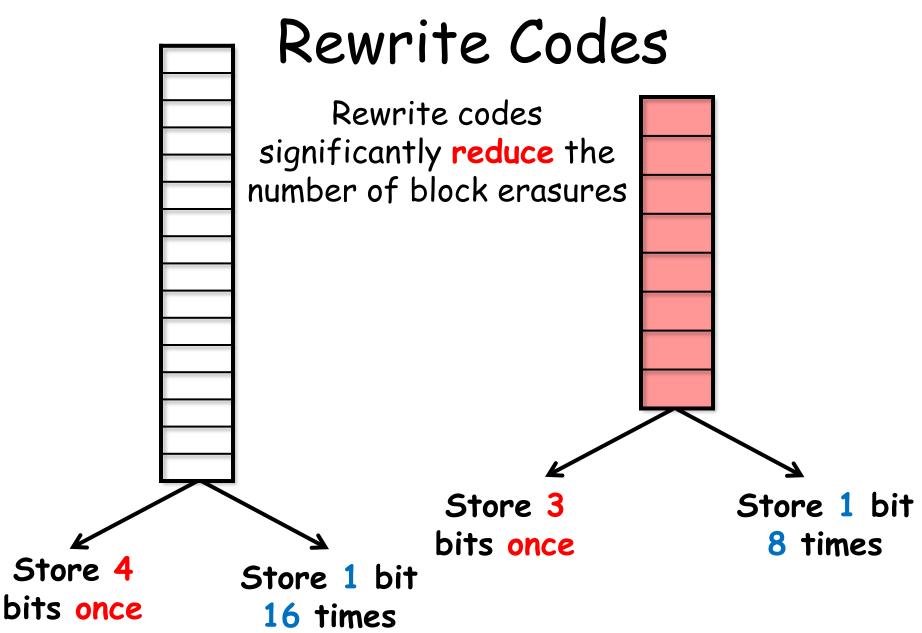

# Flash Memory Constraints

- The lifetime/endurance of flash memories corresponds to the number of times the blocks can be erased and still store reliable information

- Usually a block can tolerate ~10<sup>4</sup>-10<sup>5</sup> erasures before it becomes unreliable

- The Goal: Representing the data efficiently such that block erasures are postponed as much as possible Rewriting codes

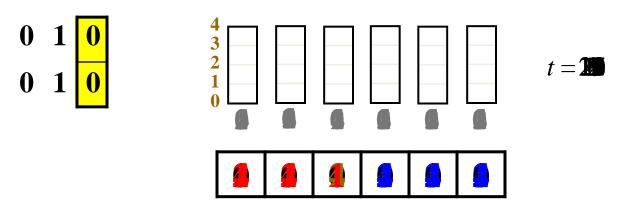

## Write-Once Memories (WOM)

- Introduced by Rivest and Shamir, "How to reuse a write-once memory", 1982

- The memory elements represent bits (2 levels) and are irreversibly programmed from '0' to '1'

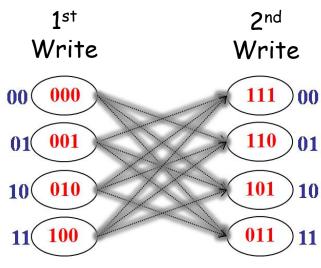

| Bits Value | 1 <sup>st</sup> Write | 2 <sup>nd</sup> Write |  |  |

|------------|-----------------------|-----------------------|--|--|

| 00         | 000                   | 111                   |  |  |

| 01         | 001                   | 110                   |  |  |

| 10         | 010                   | 101                   |  |  |

| 11         | 100                   | 011                   |  |  |

## Write-Once Memories (WOM)

• Examples:

| data | Memory          | data |                 |    | Bits Value 1 <sup>st</sup> Write            |     | 2 <sup>nd</sup> Write |  |  |

|------|-----------------|------|-----------------|----|---------------------------------------------|-----|-----------------------|--|--|

|      | State           |      | State           | 00 |                                             | 000 | 111                   |  |  |

|      |                 |      |                 | 01 |                                             | 001 | 110                   |  |  |

|      |                 |      |                 | 10 |                                             | 010 | 101                   |  |  |

|      |                 |      |                 | 11 |                                             | 100 | 011                   |  |  |

| data | Memory<br>State | data | Memory<br>State |    | 1 <sup>st</sup> 2 <sup>n</sup><br>Write Wri |     |                       |  |  |

|      |                 |      |                 |    |                                             |     |                       |  |  |

|      |                 |      |                 | 00 | 00 000 (111) 00 (111) 00 (110) 01           |     |                       |  |  |

01

10

010

11( 100

#### The problem:

What is the total number of bits that is possible to write in **n** cells in **t** writes? 110

101

011

01

10

11

# Binary WOM-Codes

- An [n,t;M<sub>1</sub>,...,M<sub>t</sub>] t-write WOM-code has n cells and guarantees any t writes of alphabet size M<sub>1</sub>,...,M<sub>t</sub> by programming cells from 0 to 1 – Example: the Rivest-Shamir code is

- The sum-rate of the WOM-code is  $R = (\Sigma_1^+ \log M_i)/n$

- Example: the Rivest-Shamir sum-rate is

- **Remark**: There are two cases:

- Individual rates on each write must all be the same (fixed-rate)

- Individual rates are allowed to be different (unrestricted-rate)

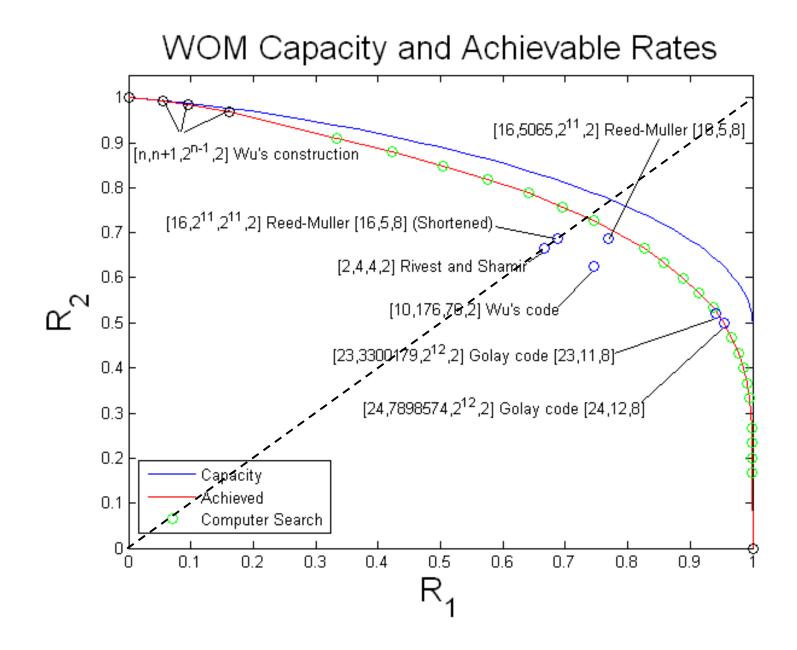

# WOM Capacity

- Capacity region (Heegard 1986, Fu and Han Vinck 1999)  $C_{t-WOM} = \{(R_1, ..., R_t) | R_1 \leq h(p_1), R_2 \leq (1-p_1)h(p_2), ..., R_2 \leq (1-p_1)h(p_2), ..., R_{t-1} \leq (1-p_1)\cdots(1-p_{t-2})h(p_{t-1}), R_t \leq (1-p_1)\cdots(1-p_{t-2})(1-p_{t-1})\}$

- Unrestricted-rate: Maximum achievable sum-rate is log(+1)

- Fixed-rate: There is a recursive formula to calculate the maximum achievable sum-rate

- Example:

- For two writes  $C_{2-WOM} = \{(R_1, R_2) | R_1 \leq h(p), R_2 \leq (1-p)\}$

- The maximum sum-rate is max<sub>p</sub>{h(p)+1-p}=log3

- The max fixed-rate sum-rate is 1.54

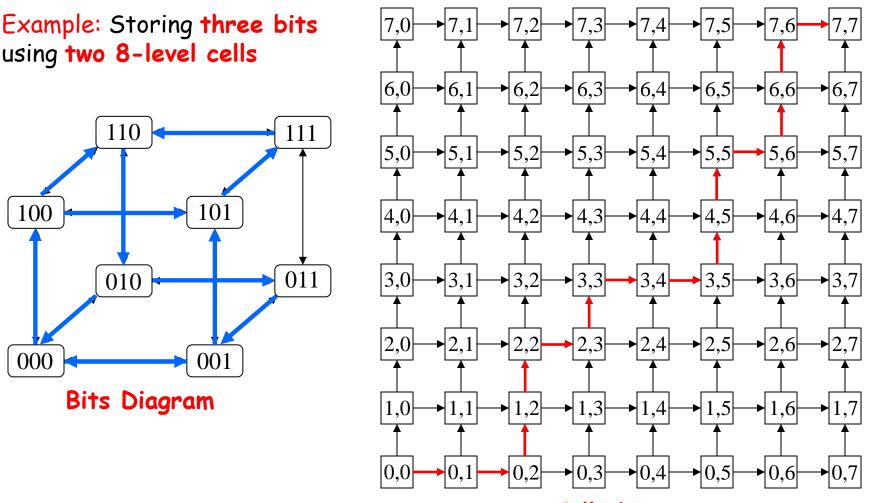

# Non-Binary WOM Codes

- Definition: An [n,t; M<sub>1</sub>,...,M<sub>t</sub>]<sub>q</sub> t-write WOM code is a coding scheme that consists of n q-ary cells and guarantees any t writes of alphabet size M<sub>1</sub>,...,M<sub>t</sub> only by increasing the cell levels

- The sum-rate of the WOM-code is  $R = (\sum_{i=1}^{t} \log M_i)/n$

# WOM Capacity

- The capacity of non-binary WOM-codes was given by Fu and Han Vinck, '99

- The maximal sum-rate using t writes and q-ary cells is

$$C = \log \binom{t+q-1}{q-1}$$

• There is no tight upper bound on the sum-rate in case equal amount of information is written on each write

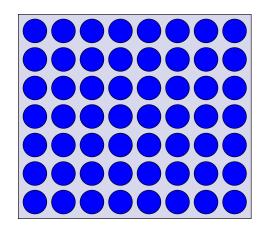

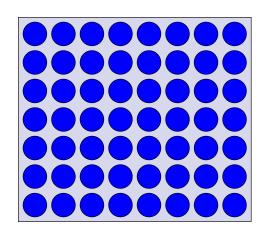

# Flash/Floating Codes

- k bits (more generally symbols) are stored using n cells

- A write is a change  $0 \to 1$  or  $1 \to 0$  of one of the k bits

- Definition Flash Codes: An (n, k, t), Flash Code is a coding scheme that accommodates <u>any sequence of up to t writes</u> of k bits, using n q-level cells, in such a way that a block erasure is never required.

- Goal: Given k, n, q, maximize the number of writes t

## Flash/Floating Codes

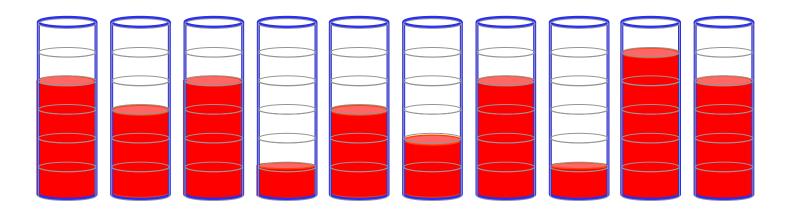

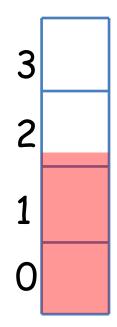

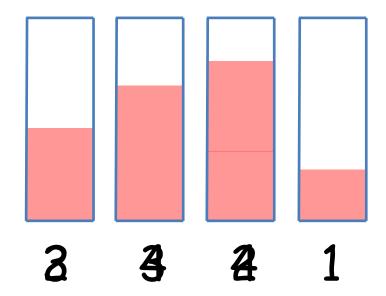

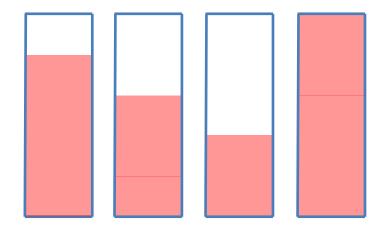

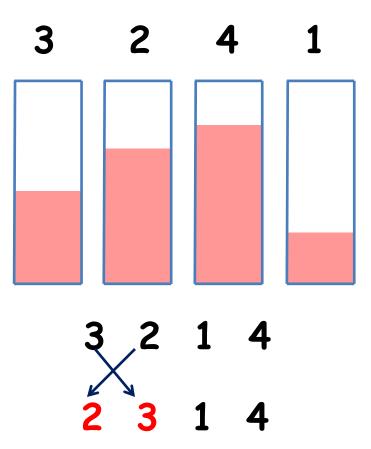

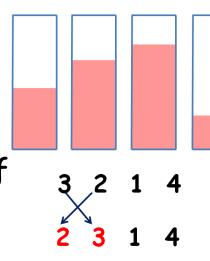

**Cells Diagram**

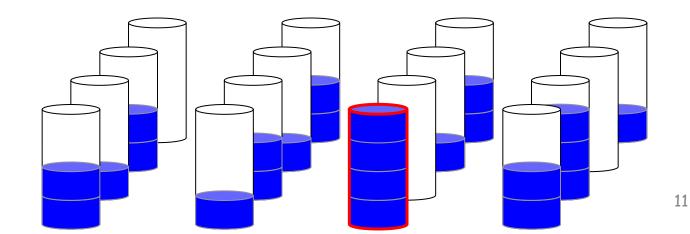

#### Example - Two Bits Construction

- Every cell is filled to the top before moving to the next one

- When the cells coincide, the last cell represents two bits. The cell's residue modulo 4 sets the bits value:

0 - (0,0) 1 - (0,1) 2 - (1,0) 3 - (1,1)

- The maximum number of writes (worst case) is n(q-1) - [(q-1)/2] (optimal) before erasing is required.

# Trajectory Codes

- Flash/floating codes suffer from a restricted rewrite model - on each rewrite, only a single bit can be updated

- Trajectory codes extend this model Jiang, Langberg, Schwartz, Bruck, "Universal Rewriting in Constrained Memories", ISIT 09'

- The update transitions are depicted in a graph

- This extended model can fit all type of codes: flash/floating codes, buffer codes, rank modulation, WOM codes

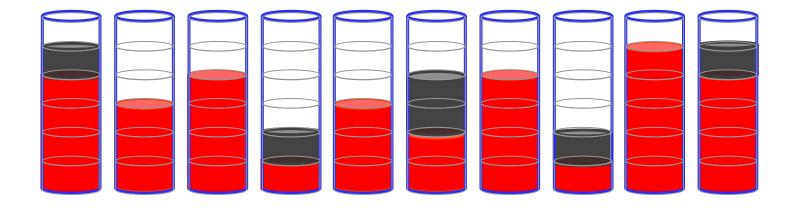

- Many storage applications, e.g. flash memories, phase-change memories and more, share the following common properties:

- Cells have multiple levels: 0,1,...,q-1

- Errors have an asymmetric behavior

- Many storage applications, e.g. flash memories, phase-change memories and more, share the following common properties:

- Cells have multiple levels: 0,1,...,q-1

- Errors have an asymmetric behavior

- If a cell error occurs, then the cell level increases (or decreases) by at most / levels

- Many storage applications, e.g. flash memories, phase-change memories and more, share the following common properties:

- Cells have multiple levels: 0,1,...,q-1

- Errors have an asymmetric behavior

- If a cell error occurs, then the cell level increases (or decreases) by at most / levels

- Flash memories

- Cells increase their level during the programming process due to over-shooting

- Cells decrease their level due to data retention

- Errors become more prominent as the device is cycled

- Phase change memories

- The drift in these memories changes the cells' levels in one direction

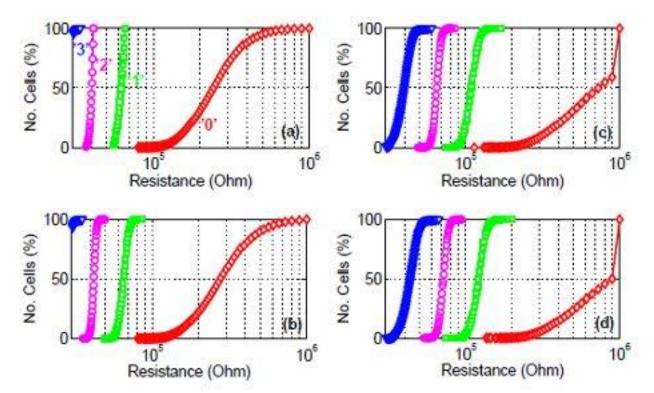

Time evolution of programmed resistance distributions of 200 kcells due to drift: (a) as programmed, and (b)  $40\mu s$ , (c) 1000s, (d) 46,000s after programming.

Figure from: N. Papandreou, H. Pozidis, T. Mittelholzer, G. F. Close, M. Breitwisch, C. Lam, and E. Eleftheriou, "Drift-Tolerant Multilevel Phase-<sup>9</sup>Change Memory", 3<sup>rd</sup> IEEE Memory Workshop, May 2011

# The Leakage Problem

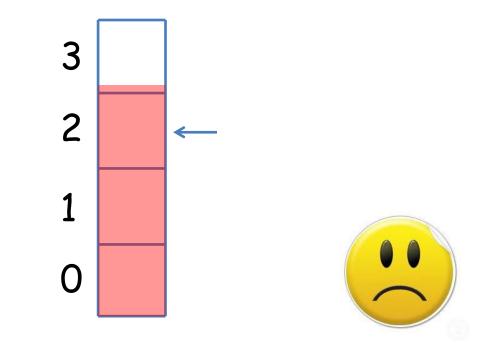

#### Error!

# The Overshooting Problem

Need to erase the whole block

### Possible Solution -Iterative Programming

Slow...

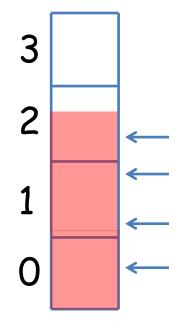

# Relative Vs. Absolute Values

# Less errors More retention

#### $(\mathbf{I})$

#### Jiang, Mateescu, Schwartz, Bruck, "Rank modulation for Flash Memories", 2008

#### The New Paradigm Rank Modulation

Absolute values  $\rightarrow$  Relative values

Single cell  $\rightarrow$  Multiple cells

Physical cell  $\rightarrow$  Logical cell

# Rank Modulation

Ordered set of **n** cells

Assume discrete levels

Relative levels define a permutation

Basic operation: push-to-the-top

Overshoot is not a concern

Writing is much faster

Increased reliability (data retention)

## Gray Codes for Rank Modulation

The problem: Is it possible to transition between all permutations?

Find cycle through n! states by push-to-the-top transitions

3

:les

Transition graph, n=3

n=3

3 cycles

3

2

1

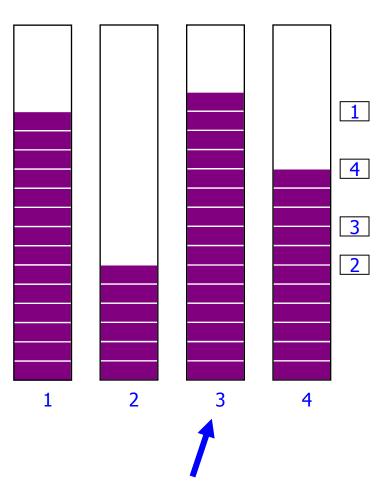

# Multiple Cells Permutation

#### Goal: Guarantee large number of rewrites

# Multiple Cells Permutation

#### Example:

- n=4 cells q=5 levels in each cell

- p = 3,2,1,4 c = 4,3,2,5 p = 1,2,3,4 c = 0,1,2,3

- c = 0,0,0,0

#### T=2 writes

#### Goal: Guarantee large number of rewrites

# Kendall's Tau Distance

- For a permutation  $\sigma$  an adjacent transposition is the local exchange of two adjacent elements

- For σ, π∈S<sub>m</sub>, d<sub>τ</sub>(σ, π) is the Kendall's tau distance between σ and π

- = Number of adjacent transpositions to change  $\sigma$  to be  $\pi$

$\sigma = 2413 \text{ and } \pi = 2314$   $2413 \rightarrow 2143 \rightarrow 2134 \rightarrow 2314$   $d_{\tau}(\sigma, \pi) = 3$

It is called also the **bubble-sort** distance The Kendall's tau distance is the number of pairs that do not agree in their order

## Other Types of Non-volatile Memories

- Phase Change Memories (PCM)

- STTRAM

- MRAM

- Memristors

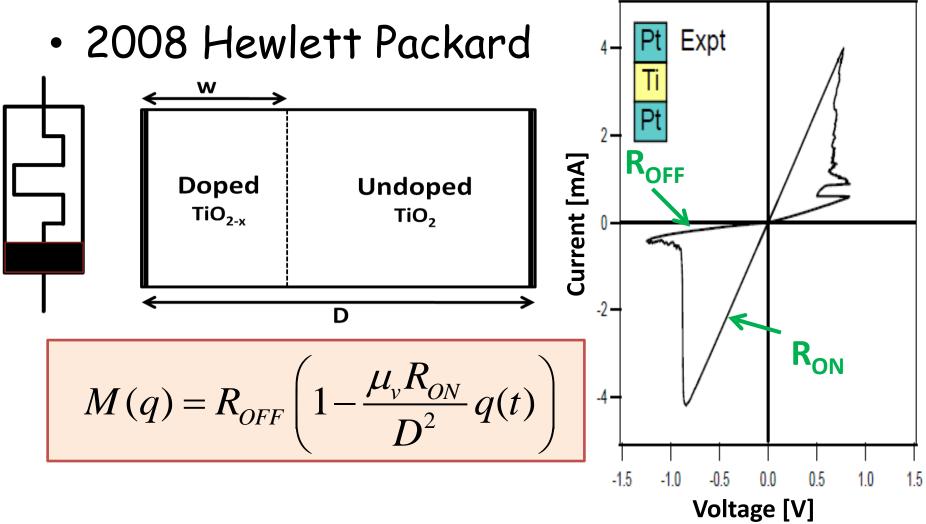

## **Practical Memristors**

D.B. Strukov et al, "The missing memristor found," Nature, 2008

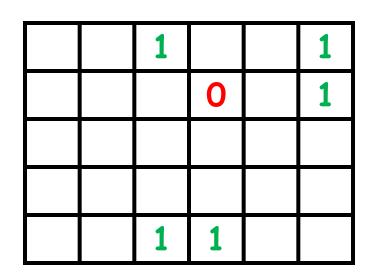

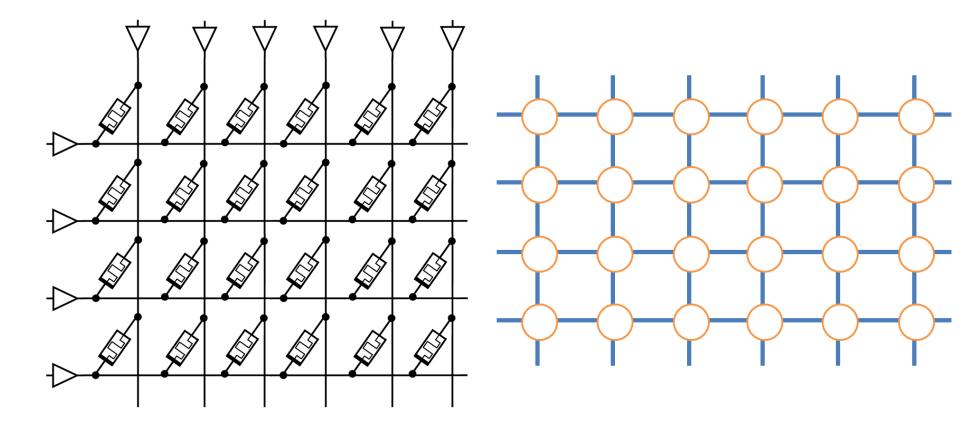

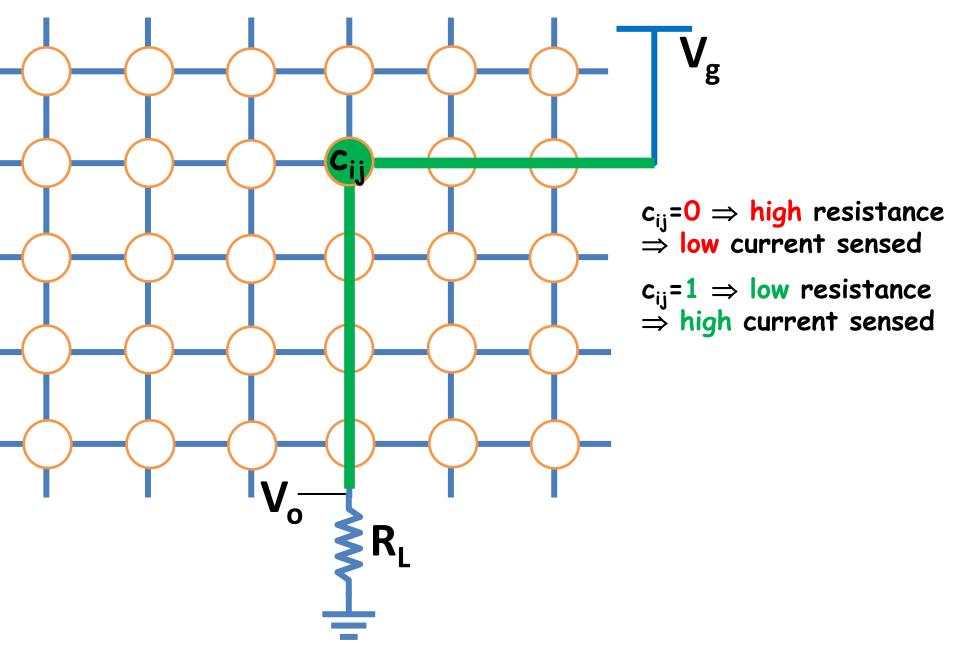

# Crossbar Arrays

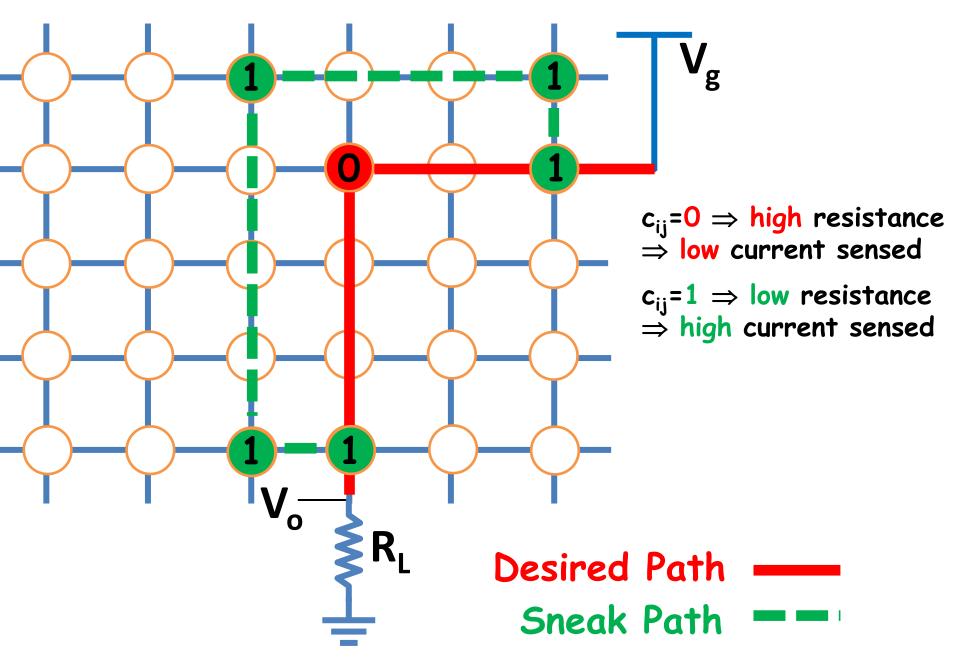

#### Sneak Path

- An array A has a sneak path of length 2k+1 affecting the (i,j) cell if

- a<sub>ij</sub>=0

- There exist  $\mathbf{r}_1, \dots, \mathbf{r}_k$  and  $\mathbf{c}_1, \dots, \mathbf{c}_k$  such that  $\mathbf{a}_{ic_1} = \mathbf{a}_{r_1c_1} = \mathbf{a}_{r_1c_2} = \dots = \mathbf{a}_{r_kc_k} = \mathbf{a}_{r_kj} = \mathbf{1}$

- An array A satisfies the sneak-path constraint if it has no sneak paths and then is called a sneak-path free array